ADC(Analog to Digital Converter)란,

이전 포스팅에서 Analog와 Digital 신호에 대한 개념을 어느정도 익혔다면 우리가 데이터 수집(Data Acquisition, DAQ)을 하는 과정에서 센서의 값을 PC에서 본다라고 하면 PC에서 보는 값은 디지털 값이라고 생각할 수 있습니다. DAQ를 처음 배울 때 이런 고민을 많이 했었죠..

센서가 물리적인 현상을 전기적인 신호로 바꿔준다는 것은 알겠는데,

어떻게 DAQ 장비는 이 전기적인 신호의 값을 알 수 있는가?

바로 ADC인데요. 관련 전공자 분들은 쉽게 아쉴 수 있지만 모르시는 분들을 위해 이번 시간에는 ADC가 무엇인지 살펴보도록 하겠습니다.

ADC(Analog to Digital Converter)란

ADC란, Analog to Digital Converter를 말하며 아날로그 신호를 디지털로 변환시켜주는 장치를 말합니다.

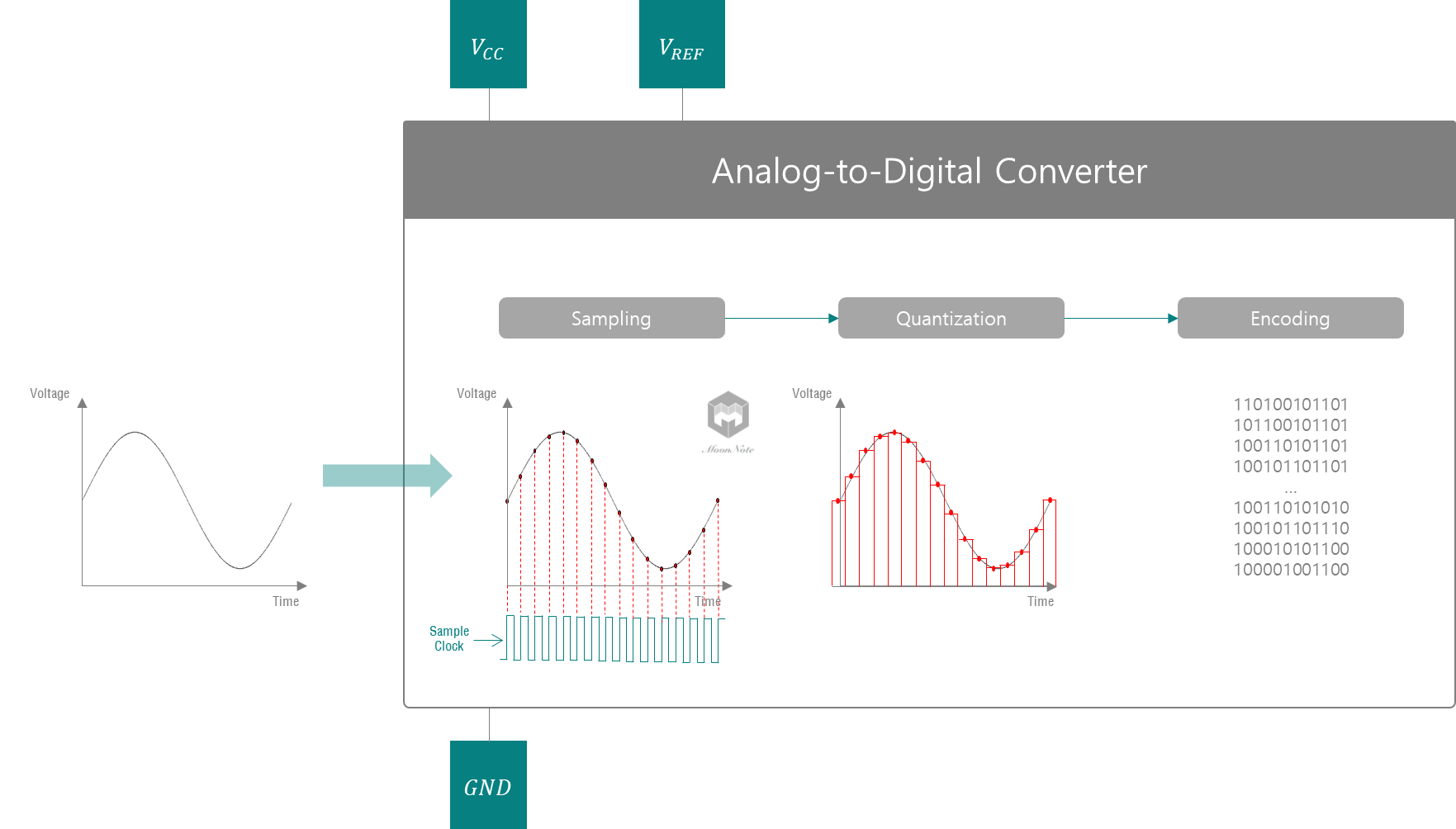

아날로그 신호를 측정한다라고 하였을 때 DAQ 장비의 AI 채널들은 바로 이 ADC와 연결이 되어있어서 AD Converting을 하게 됩니다. 이후 변환된 디지털 값을 PC로 전달하여 우리가 소프트웨어에서 보는 것이죠. DAQ 시스템 구성을 보면 "[센서]-[DAQ]-[PC]"순으로 연결이 되었었는데요. DAQ 디바이스에서 ADC의 과정을 조금 더 살펴보면 아래 이미지와 같은 순서라고 보시면 되겠습니다.

ADC에서 아날로그 신호를 디지털화 하기 위해 표본화(Sampling), 양자화(Quantization), 부호화(Encoding) 총 3 단계 과정을 거치게 됩니다.

표본화(Sampling)

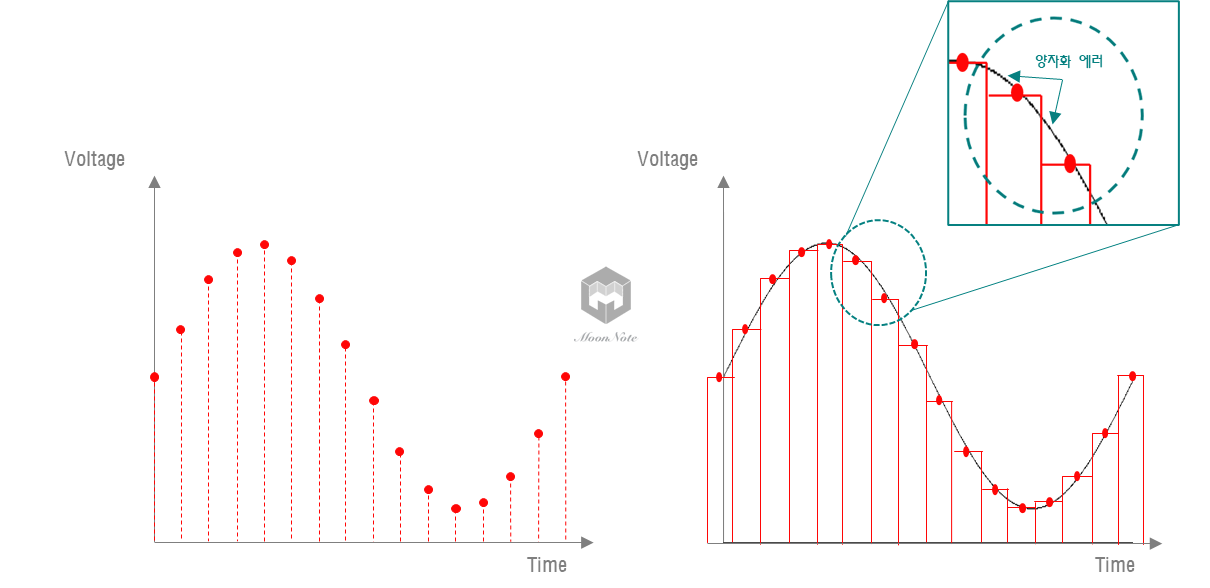

연속적인 아날로그 신호를 시간축을 따라 이산 값으로 변환하는 과정을 표본화(또는 샘플링이라고 부름)라고 합니다. 샤논(Shannon)의 표본화 정리에 따르면 신호 주파수의 2배 이상의 빈도로 샘플링을 해야지 원신호를 복원할 수 있다고 하는데 샘플링과 관련된 사항은 이후 포스팅 글에서 다루도록 하겠습니다.

양자화(Quantization)

샘플링이 시간 축(X-Axis)이었다면 양자화는 진폭 축(Y-Axis)을 따라 이산 값으로 변환하는 과정을 양자화(Quantization)이라고 합니다. 양자화 레벨로 간격을 나누어 뽑은 표본 값을 미리 정해진 값에서 가장 가까운 값으로 변환하게 됩니다. 표현할 수 있는 값의 단위가 8 bit(0~255) 면 256개, 10 bit(0~1023) 면 1024개로 더 정밀하게 표현되죠. 하지만 양자화 과정에서 실제 값과 오차가 발생할 수밖에 없는데 이를 양자화 에러라고 합니다.

부호화(Encoding)

표본화와 양자화를 통해 나온 숫자들을 2진수(Binary)로 바꾸어주는 작업을 말합니다.

ADC 성능

ADC에서 성능을 나타내는 주요 항목들로 분해능, 입력 전압 범위, 샘플링 속도입니다. 어떤 의미인지 하나씩 살펴보겠습니다.

분해능(Resolution)

신호를 얼마나 잘게 쪼갤 수 있는지 나타내는 능력을 말하며 n bits 형태로 표현합니다. bit 수가 커지면 커질수록 '분해능이 좋다'라고 표현하며 이는 아날로그 신호를 얼마나 민감하게 읽어 들일 수 있는가를 나타내는 척도가 됩니다. 당연히 bit 수가 높으면 높을수록 가격이 비싸고 좋지만 이것을 처리하는 마이크로프로세스 워드 길이와 연관되기에 응용 분야에서 적합한 ADC로 선택할 필요가 있습니다.

입력 전압 범위(Full Scale Range)

말 그대로 기기를 정상 상태로 사용할 수 있는 최대 전압 입력 범위를 말합니다. ADC는 입력으로 Vcc 전압 이하의 전압 값을 입력으로 받을 수 있는데 이를 ADC가 가지고 있는 n bits 스펙만큼 쪼개어 디지털 값으로 표현할 수 있습니다. 따라서 보통 FSR이라고 표기하며 'Full Scale Range'라는 의미입니다.

샘플링 속도(Sampling Rate)

샘플 속도 또는 샘플링 속도라고 부르며 SPS라고 표기하기도 합니다. 1초를 기준으로 몇 개의 샘플을 수집할 것인지 나타내는 말로 실제 A/D 변환을 수행하는데 필요한 시간(변환 시간(Conversion Time)이라고도함)을 말합니다. 단위는 'S/s'로 표현하기도 하는데 '샘플(Sample)/시간(sec)'의 의미입니다. (또는 그냥 몇 Hz로 샘플링한다라고 말하기도 합니다.)

기타 특성

아래쪽에서 설명드리겠지만 ADC의 종류도 다양합니다. 특정 ADC의 경우 S/H 또는 T/H 회로를 사용하는데요. 샘플/홀드 또는 트랙/홀드라고하여 A/D 컨버팅 중에 입력 전압이 변동하여 출력에 대한 불확실성을 방지하기 위해서 아날로그 스위치, 콘덴서, 버퍼 등으로 구성된 회로라고 생각하시면 되겠습니다.

이 외에도 INL(Integral Nonlinearity Error), DNL(Differential Nonlinearity Error), Aperture Error, 오프셋 오차(Offset Error), 이득 오차(Gain Error), A/D 전달 함수, SNR, ENOB 등 많이 있지만 이번 포스팅에서는 간략하게만 소개드리고 궁금하신 분들은 추가 검색해보셔도 좋을 듯하네요.

- INL(Integral Nonlinearity Error) : 이상적인 출력과 얼마나 다른지를 나타내는 에러

- DNL(Differential Nonlinearity Error) : 디지털로 변환되는 아날로그 입력 범위가 일정하지 않아 발생하는 에러

- Aperture Error : 신호를 Sample and Hold 할 때 걸리는 미세한 시간 에러

- 오프셋 오차(Offset Error) : 0V와 DIFF전압이 ADC에 들어올 때 이상적인 값과 실제 값의 편차

- 이득 오차(Gain Error) : FSR에서의 이상적인 기울기와 실제 기울기 사이의 편차

- A/D 전달 함수 : 입력 전압과 출력 디지털 값을 XY그래프로 '계단 모양'으로 그려 '함수적 관계성'을 나타낸 것

- SNR(Signal-to-Noise Ratio) : 신호 대 잡음비

- ENOB(Effective Number of Bits) : 유효 비트 수

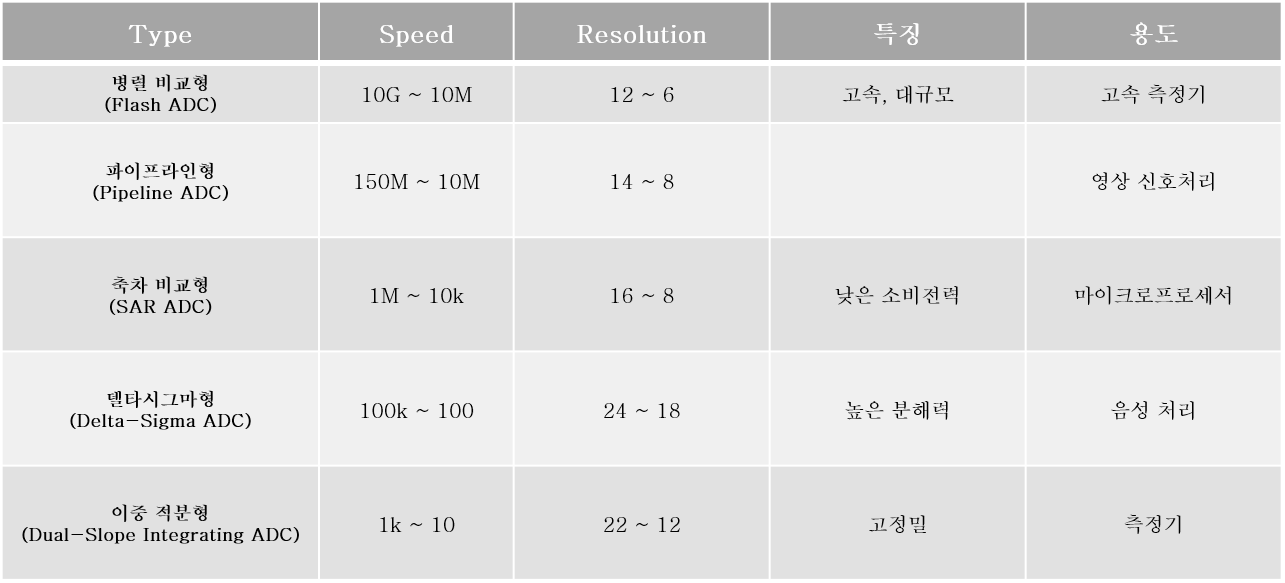

ADC 종류

ADC 회로의 구조에 따라 변환 방식이 차이나며 그에 따른 종류도 나뉘게 됩니다. 각 타입별 스펙 및 자세한 사항은 아래의 테이블 표와 같습니다.

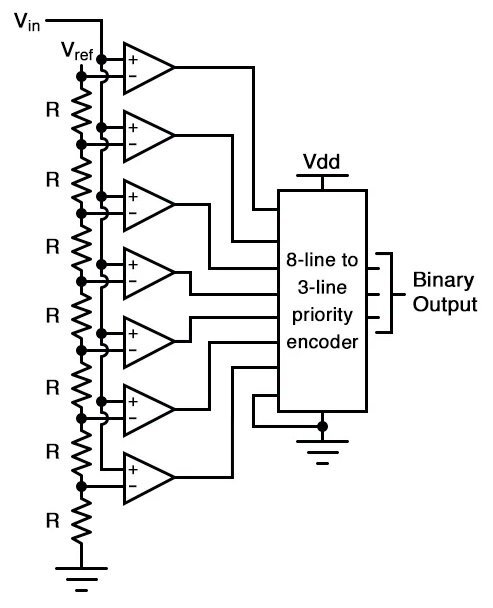

병렬 비교형(Flash ADC)

회로 소자를 병렬 구조로 배치하여 각각의 비교기 +단자에는 측정 신호를 입력하고 - 단자에는 그림과 같이 저항으로 나뉘어진 측정 범위에 해당하는 실제 전압을 입력합니다. 장점은 한 단계에 비교가 완료되므로 매우 빠른 변환이 가능하다는 것이며 단점은 높은 분해능을 갖게할 수록 비교기의 수가 많아지고 회로가 복잡해지므로 가격이 비싸진다는 것이다. Op-Amp가 사용되며 가격이 비싸지만 매우 빠른 처리 속도를 요구하는 분야에서 사용됩니다.

파이프라인형(Pipeline ADC)

파이프라인은 한 데이터 처리 단계의 출력이 다음 단계의 입력으로 이어지는 형태로 연결된 구조를 말합니다. 아래의 이미지처럼 각 단계는 연속적인 단계를 가지고 있는데 S/H와 낮은 분해능을 가진 ADC와 DAC, Interchange Amplifier를 포함한 Summing 회로를 포함하고 있습니다. 파이프라인 ADC의 특징은 칩의 면적과 전력 소모가 크게 줄어들고 SHA(Sample-and-Hold Amplifier)회로가 필요하다는 것입니다. 일괄 동작으로 고속 변환이 가능하고 고주파 신호에 대한 광범위한 Dynamic Range 를 가지지만 파이프라인이 꽉 차기 전의 데이터는 소용없기 때문에 지연이 발생하게 됩니다. 따라서 프로그램시 주의가 필요합니다.

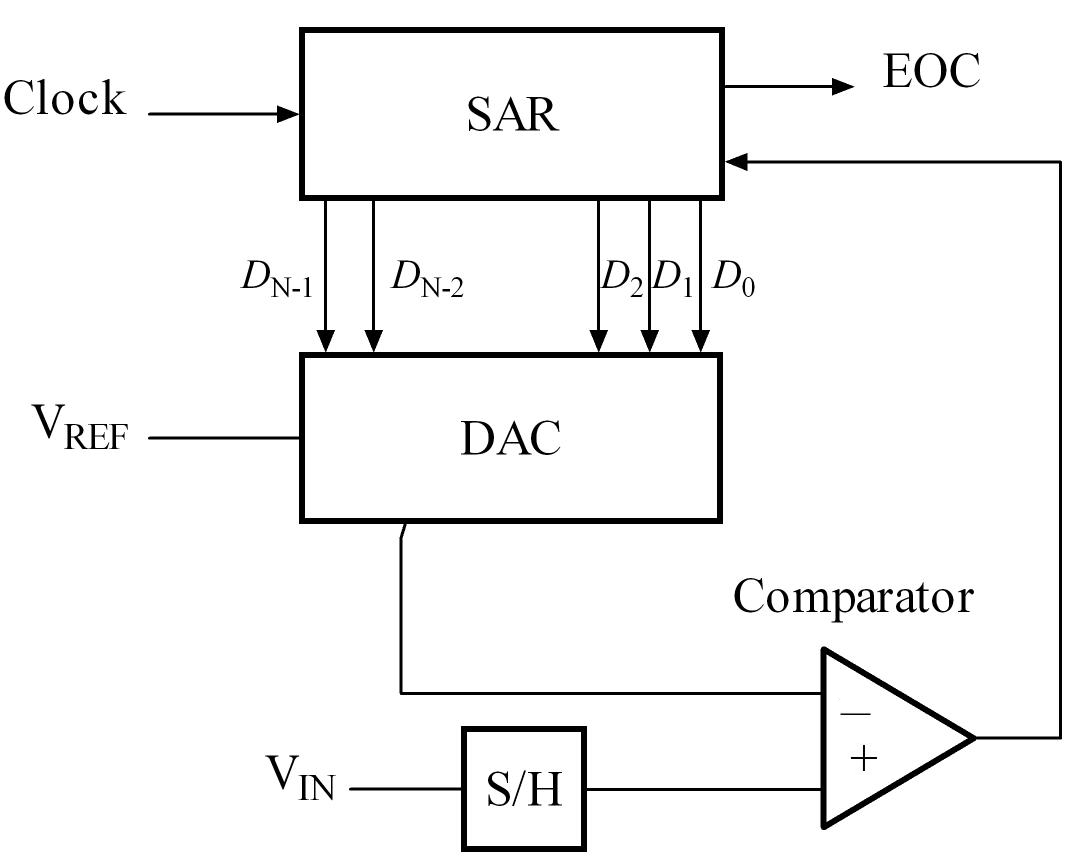

축차 비교형(SAR, Successive Approximation Register ADC)

SAR ADC는 하나의 비교기를 여러번(bit 개수만큼) 비교하여 결과를 얻어내는 방식입니다. 최상위 비트부터 순서대로 하위 비트쪽으로 수정하여 가는 방법으로 DAC의 출력을 훨씬 빨리하여 아날로그 입력 전압에 근사시킵니다. SAR 방식의 특징은 bit 개수만큼 반복된다는 것인데 Flash ADC와 비교하였을 때 최대 N배의 시간이 걸리고 최대 샘플링에 한계가 있다는 점입니다. 하지만 비교적 변환 시간이 빠르고 회로가 간단한 저가형이기 때문에 가장 널리 사용되고 있습니다. SAR 역시 변환 중에 입력 전압이 일정해야하므로 S/H가 반드시 필요한 타입입니다.

델타시그마형(Delta-Sigma ADC)

델타시그마 ADC는 신호의 값을 대강 예상하여 오차를 구한 다음 누적된 오차를 이용하여 오차를 보정해 나가는 방식입니다. 이 원리에 의하면 누적 오차 값이 유한하다면, 입력 신호의 평균 값과 출력 신호의 평균 값은 같아지게 됩니다. 매우 높은 해상도(18-24 bits)를 가지며 정밀 산업 측정, 열전대 온도 측정 및 음성 대역 어플리케이션에 적합합니다. 단점은 고해상도를 위한 낮은 샘플링 속도가 되겠습니다.

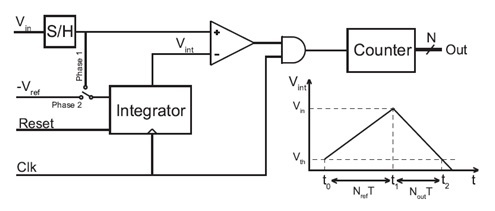

이중 적분형(Dual-Slope Integrating ADC)

일정한 시간동안 아날로그 입력 신호를 적분하고 나서 계수기를 리셋한 후 다시 기준 전압을 적분기의 출력이 0이 될 때까지 그 시간을 측정하는 방식입니다. 적분 특성상 잡음에 대해서 안정된 변화 특성을 가지지만 2번의 적분 시간 때문에 변환 시간이 길다는 단점이 있습니다. 보통 저속 동작을하는 시스템에 많이 사용됩니다.

※ 이 글이 도움이 되었다면 "🤍공감" 버튼을 클릭해주세요. 클릭 한번이 글 쓰는데 큰 힘이 됩니다.